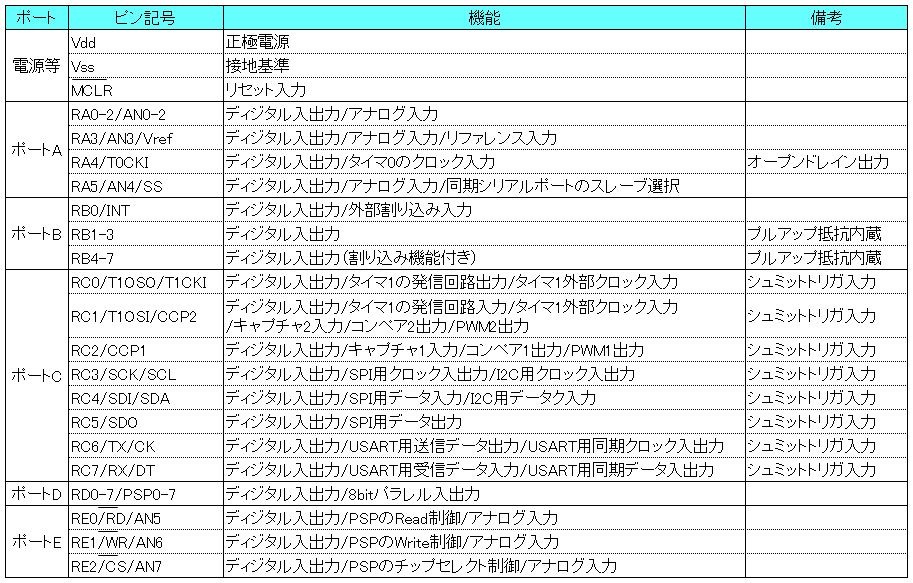

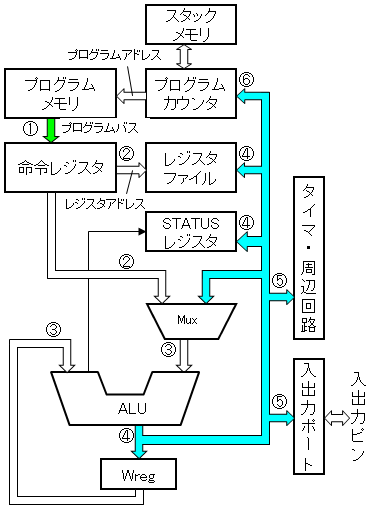

プログラムメモリ

program memory |

プログラムを格納するメモリ. |

スタックメモリ

stack memory |

サブルーチンや割り込みの戻り番地を格納する専用メモリ.

命令では操作できない. |

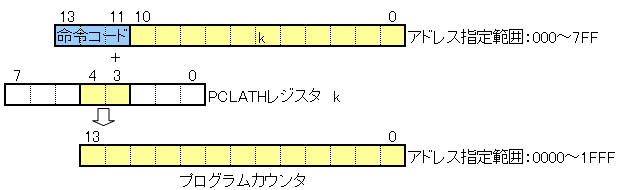

プログラムカウンタ

program counter |

プログラムの実行を制御するカウンタ.プログラムカウンタの内容がアドレスとなり,そのアドレスで指定されたプログラムメモリ内の命令が,次に実行される命令となる. |

レジスタファイル

file register |

レジスタ群により構成されるデータ格納用メモリ.

PIC 特有のアーキテクチャ.

2 つの領域からなり,1 つは汎用のデータ領域であり,プログラム内で使う変数領域として使用する(GPR:General Purpose Register).

もう 1 つは特別なレジスタ領域であり,SFR(Special Fanction Resister)と呼ばれ,内蔵周辺回路の動作を制御するために使用される.入出力ポートも

SFR に属する. |

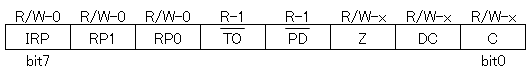

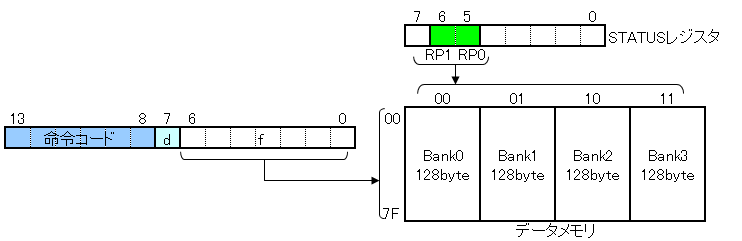

STATUSレジスタ

STATUS register |

演算結果の状態,ゼロ,Carry 等を保持するレジスタ.

条件分岐時等のフラグとして使用する. |

命令レジスタ

instruction register |

プログラムメモリから読み出された命令がセットされ,命令の種類の解読と処理が行われる. |

MUX

mutiplexer |

各命令の指示に従って各種レジスタや Wreg の内容との演算がなされる部分.

演算結果は Wreg や入出力ポートやタイマ,プログラムカウンタ等に格納される. |

ALU

arithmetic logic unit |

Wreg

working register |

演算データ一時保管用レジスタ. |

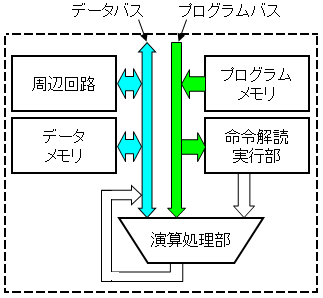

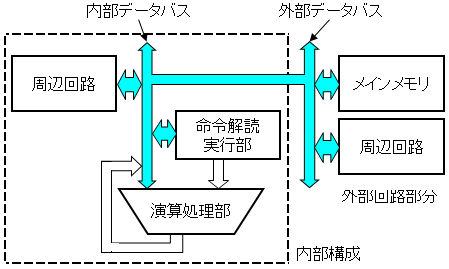

データバス

data bus |

命令実行に関係するデータを運ぶ通信路.

8 bit のデータを扱うため,8 本の線で構成されている. |

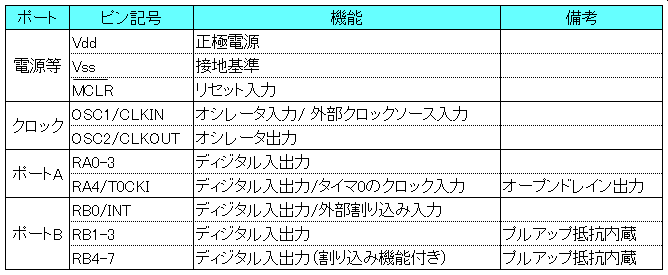

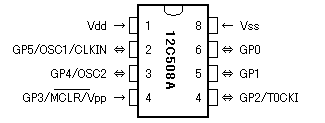

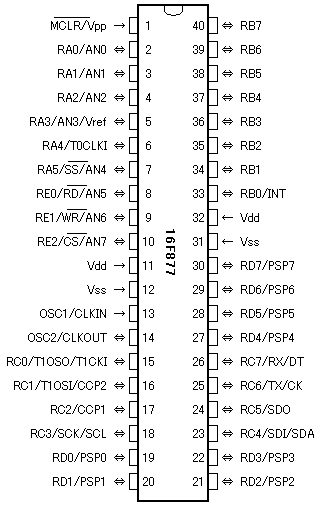

入出力ポート

I/O port |

PIC 内部に外部からデータを入力,もしくは内部のデータを外部に出力するためのポート. |

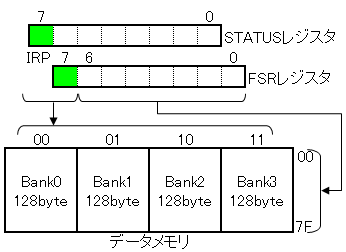

データメモリのアクセスには,直接レジスタのアドレスを指定する直接アドレッシング以外に,間接アドレッシングと言う方法がある.間接アドレッシングには,プログラムで書き換え可能な SFR

である FSR レジスタと STATUS レジスタの IRP ビットを使用する.

データメモリのアクセスには,直接レジスタのアドレスを指定する直接アドレッシング以外に,間接アドレッシングと言う方法がある.間接アドレッシングには,プログラムで書き換え可能な SFR

である FSR レジスタと STATUS レジスタの IRP ビットを使用する.